MAX 10 FPGA设计安全和减小SEU培训

2014-10-24 Altera

MAX 10 FPGA用户闪存培训

2014-10-24 Altera

MAX 10 FPGA开发套件演示

2014-10-11 Altera

MAX 10 FPGA PLL和时钟培训

2014-10-24 Altera

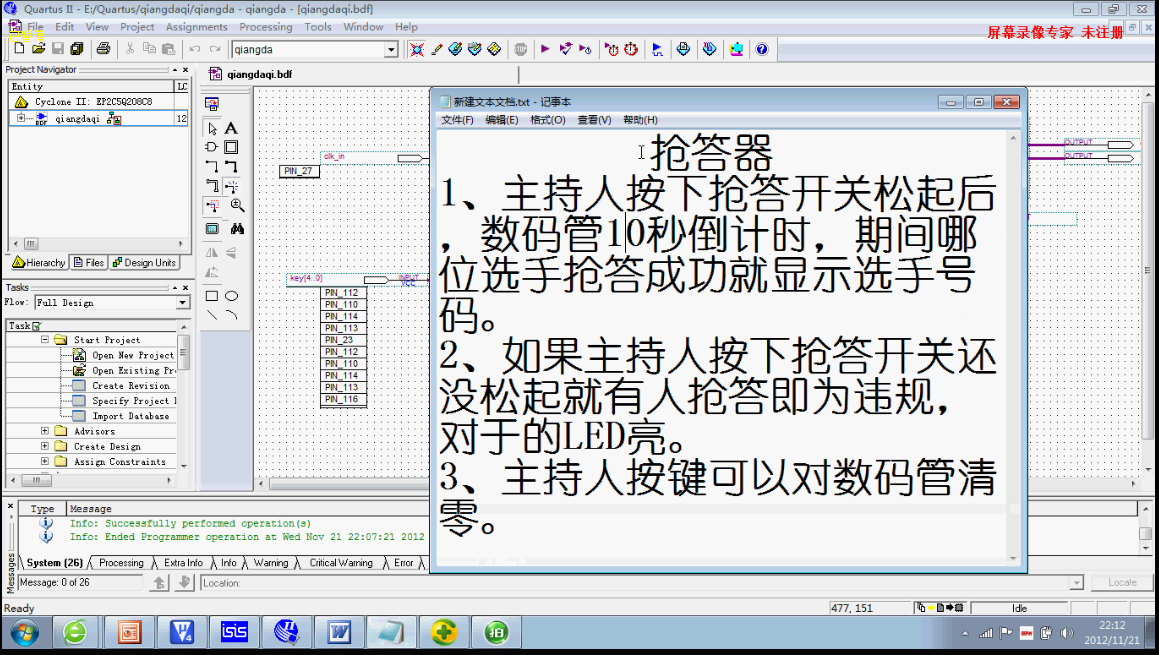

MAX 10 FPGA配置培训

2014-10-24 Altera

MAX 10 FPGA简介培训

2014-10-24 Altera

MAX 10 FPGA模拟模块培训

2014-10-24 Altera

MAX 10 FPGA GPIO培训

2014-10-24 Altera

赛灵思的UltraScale架构 - 业界首款ASIC级可编程架构

2014-02-14 Xilinx

Virtex-7 2000T的功能

2014-02-14 Xilinx

为什么自适应均衡器是收发器设计关键的两大原因

2014-02-13 Xilinx